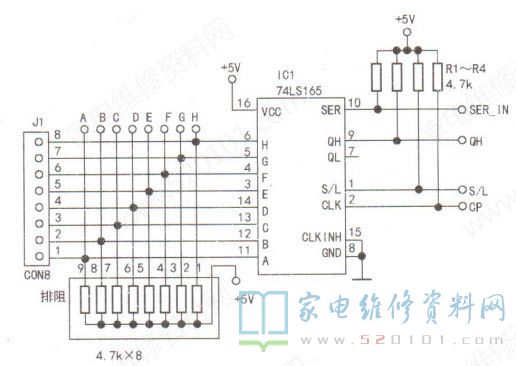

概述:74LS165是一款8位并行输入、串行输出移位寄存器,其典型应用电路如图1所示。A~H:并行数据输入端;QH、QL:串行数据输出端;CP:时钟输入端。CLKINH:时钟禁止端,当该端为低电平时,允许时钟输入;S/L:移位与置位控制端;SER. IN:扩展多个74LS165的首尾连接端。当①脚为低电平时,芯片将输入数据A~H分别存入内部对应的寄存器中,随即①脚变为高电平。当②脚接收到8个时钟脉冲后,并行数据从⑨脚( QH )和⑦脚( QL)串行移出(⑦脚移出的数据是反相的)。

一、74LS165引脚功能和应用电路

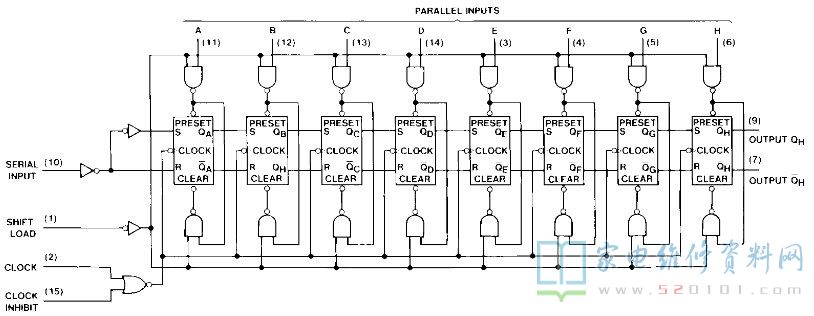

二、74LS165逻辑图

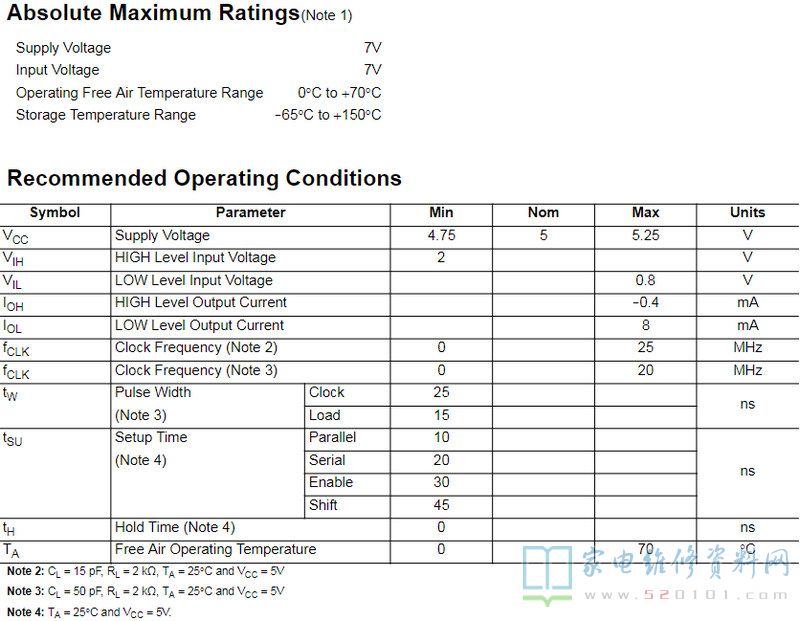

三、74LS165极限参数和电气参数

网友评论