其特点有:

(1)12位分辨率A/D转换器;

(2)在工作温度范围内10μs转换时间;

(3)11个模拟输入通道;

(4)3路内置自测试方式;

(5)采样率为66kbps;

(6)线性误差+1LSB(max)

(7)有转换结束(EOC)输出;

(8)具有单、双极性输出;

(9)可编程的MSB或LSB前导;

(10)可编程的输出数据长度。

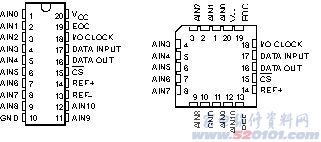

TLC2543的引脚排列如下图

TLC2543的使用方法:

1 控制字的格式

控制字为从DATAINPUT端串行输入的8位数据,它规定了TLC2543要转换的模拟量通道、转换后的输出数据长度、输出数据的格式。其中高4位(D7~D4)决定通道号,对于0通道至10通道,该4位分别为0000~1010H,当为1011~1101时,用于对TLC2543的自检,分别测试(VREF++VREF-)/2、VREF-、VREF+的值,当为1110时,TLC2543进入休眠状态。低4位决定输出数据长度及格式,其中D3、D2决定输出数据长度,01表示输出数据长度为8位,11表示输出数据长度为16位,其他为12位。D1决定输出数据是高位先送出,还是低位先送出,为0表示高位先送出。D0决定输出数据是单极性(二进制)还是双极性(2的补码),若为单极性,该位为0,反之为1。

2 转换过程

上电后,片选CS必须从高到低,才能开始一次工作周期,此时EOC为高,输入数据寄存器被置为0,输出数据寄存器的内容是随机的。

开始时,CS片选为高,I/O CLOCK、DATA INPUT被禁止,DATA OUT 呈高阻状,EOC为高。使CS变低,I/OCLOCK、DATAINPUT使能,DATAOUT脱离高阻状态。12个时钟信号从I/OCLOCK端依次加入,随着时钟信号的加入,控制字从DATAINPUT一位一位地在时钟信号的上升沿时被送入TLC2543(高位先送入),同时上一周期转换的A/D数据,即输出数据寄存器中的数据从DATAOUT一位一位地移出。TLC2543收到第4个时钟信号后,通道号也已收到,此时TLC2543开始对选定通道的模拟量进行采样,并保持到第12个时钟的下降沿。在第12个时钟下降沿,EOC变低,开始对本次采样的模拟量进行A/D转换,转换时间约需10μs,转换完成后EOC变高,转换的数据在输出数据寄存器中,待下一个工作周期输出。此后,可以进行新的工作周期。

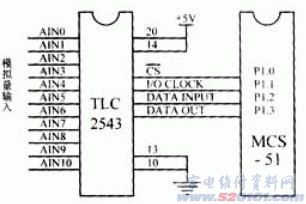

3 TLC2543与单片机的接口和采集程序

目前使用的51系列单片机没有SPI接口,为了与TLC2543接口,可以用软件功能来实现SPI的功能,其硬件接口如图2所示。本示例采用延时进行采集,故省去了EOC引脚的接口。

LC2543与51系列单片机的接口原理图

引脚参数

|

引脚 |

定义 |

I/O |

说明 |

|

1~9,11,12 |

AIN0~AIN10 |

I |

模拟量输入端。11路输入信号由内部多路器选通。对于4.1MHz的I/OCLOCK,驱动源阻抗必须小于或等于50Ω,而且用60pF电容来限制模拟输入电压的斜率 |

|

15 |

CS |

I |

片选端。在CS端由高变低时,内部计数器复位。由低变高时,在设定时间内禁止DATAINPUT和I/O CLOCK |

|

17 |

DATAINPUT |

I |

串行数据输入端。由4位的串行地址输入来选择模拟量输入通道 |

|

16 |

DATA OUT |

O |

A/D转换结果的三态串行输出端。CS为高时处于高阻抗状态, CS为低时处于激活状态 |

|

19 |

EOC |

O |

转换结束端。在最后的I/OCLOCK下降沿之后,EOC从高电平变为低电平并保持到转换完成和数据准备传输为止 |

|

10 |

GND |

地。GND是内部电路的地回路端。除另有说明外,所有电压测量都相对GND而言 | |

|

18 |

I/O CLOCK |

I |

输入/输出时钟端。I/OCLOCK接收串行输入信号并完成以下四个功能:(1)在I/O CLOCK的前8个上升沿,8位输入数据存入输入数据寄存器。(2)在I/OCLOCK的第4个下降沿,被选通的模拟输入电压开始向电容器充电,直到I/OCLOCK的最后一个下降沿为止。(3)将前一次转换数据的其余11位输出到DATA OUT端,在I/OCLOCK的下降沿时数据开始变化。(4)I/OCLOCK的最后一个下降沿,将转换的控制信号传送到内部状态控制位 |

|

14 |

REF+ |

I |

正基准电压端。基准电压的正端(通常为Vcc)被加到REF+,最大的输入电压范围由加于本端与REF-端的电压差决定 |

|

13 |

REF- |

I |

负基准电压端。基准电压的低端(通常为地)被加到REF- |

|

20 |

Vcc |

电源 |

网友评论