概述:RTL-4553采用双列14脚封装。

该芯片采用内置晶振和独特的数据方法,大大提高了时钟精度和可靠性。RTC-4553配有串行通信接口,另有30×4bit SRAM,有2000~2099的百年日历,采用14脚SOP封装,电池耗电2μA,时钟误差<3 min/年且无需调整,是仪器仪表高精度时钟的理想芯片。

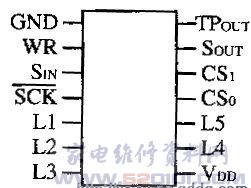

一、RTL-4553引脚功能

CS0为片选脚,低电平选中;WR为读写使能口,高为读,低为写;L1~L5为工厂出厂调整精度和测试用,使用中悬空;CS1为芯片掉电检查口,可直接与系统电源连接,芯片测到该口为低时,自动进入低功耗状态;SCK为时钟口,SIN为数据输入口,SOUT为数据输出口。另外,芯片还有1个时钟信号输出口TPOUT,该口可输出1024Hz或1/10Hz的信号,以供检测芯片的时钟精度所用。

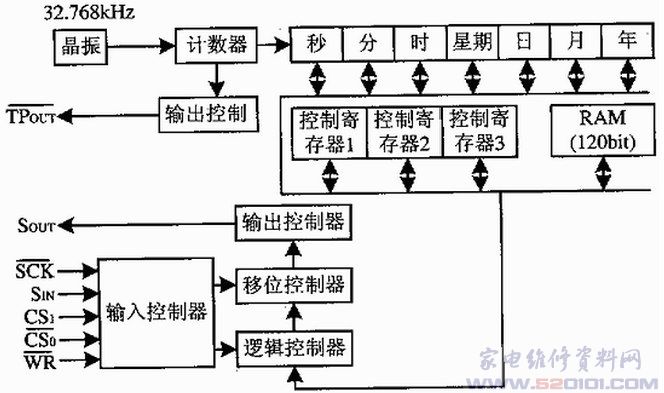

二、RTL-4553内部方框图

1 内部结构及引脚 串行 时钟芯片的内部结构如图1所示。它包含I/O控制器、移位寄存器、命令及逻辑控制器,表态RAM、实时时钟、计数器、晶振等部分。 图2为RTC-4553的引脚图。CS0为片选脚,低电平选中;WR为读写使能口高为读,低为写;L1~L5为工厂出厂调整精度和测试用,使用中悬空;

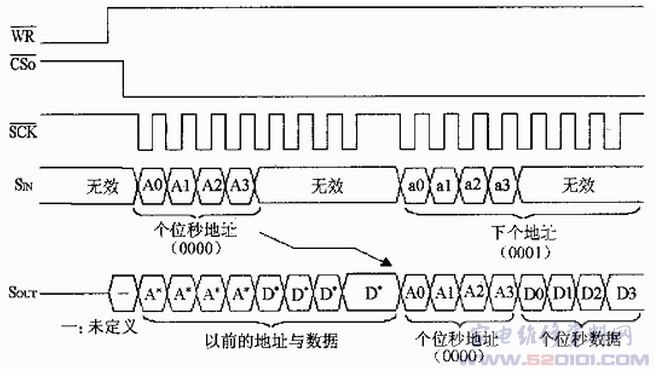

CS1为芯片掉电检查口,可直接与系统电源连接,芯片测到该口为低时,自动进入低功耗状态;SCK为时钟口,SIN为数据输入口,SOUT为数据输出口。另外,芯片还有1个时钟信号输出口TPOUT,该口可输出1024HZ或1/10HZ的信号,以供检测芯片的时钟精度所用。 2 功能及控制 2.1 寄存器 RTC-4553共有46%26;#215;4BIT寄存器。这些寄存器分3页,第1页共16个,分别为时钟寄存器和控制寄存器,如表1所列,用来存放秒、分、时、日、月、年、星期和3个特殊寄存器;第2页、第3页各有15个,共30个SRAM寄存器,页面的选择通过操作控制寄存器3的MS1、MS0位来实现。 表1 第0页第1页第2页 地址A3A2A1A0 功能说明地址A3A2A1A0 功能说明地址A3A2A1A0 0 1 2 3 4 5 6 7 8 9 0A 0B 0C 0D 0E 0F 个位秒十位秒个位分十位分个位时十位时星期个位天十位天个位月十位月个位年十位年控制寄存器1 控制寄存器2 控制寄存器3 0 1 2 3 4 5 6 7 8 9 0A 0B 0C 0D 0E 静 态 RAM 区 0 1 2 3 4 5 6 7 8 9 0A 0B 0C 0D 0E 静 态 RAM 区控制寄存器1:CNT1 TPS - CNTR 24/12 TPS——TPOUT输出时钟选择位,1输出1024HZ,0输出1/10HZ; CNTR——时钟寄存器清零标志; 24/12——1为24小时制,0为12小时制。 控制寄存器2: BUSY PONC - - BUSY——有进位溢出; PONC——初始上电检测,为1表示刚上电需校时。 控制寄存器3: - - MS1 MS0 MS1、MS0——页面选择位,00和01指向0页,10指向1页,11指向2页。 2.2 数据读出 在片选择中芯片,WR置高时,芯片处于读出状态,随着SCK脚上的时钟变化,内部寄存器的数据将出现在SOUT脚上。输入需要8个时钟,4个用来输入地址;输出数据也需要8个时钟,包括4个地址位4个数据位。数据在SCK上升沿输入,在下降沿输出。寄存器的地址由SIN脚输入,页面由MS0、MS1决定。

网友评论