概述:FT245BL是FTDI公司的一款并行FIFO双向数据传输的USB芯片,对于微处理器它提供8位并行数据总线D0~D7,对于外部主机是标准串行总线或虚拟接口,其数据传输速率最高可达1 MB/s,提供USB1.1/2.O规范的全速物理接口,支持UHCI/OHCI/EHCI主控制器。

传统USB芯片要求设计人员对USB的标准、Firmware编程及驱动程序的开发等有较深入的理解,工作量大,开发周期长,需要经验丰富的设计者才能完成;而FTDI(Future Technology DevICes Intl.Ltd.)公司推出的USB芯片FT245BL集成了微控制器,并且把实现USB通信协议的固件程序直接固化在芯片中,同时提供了PC端的没备驱动程序,用户只需进行必要的硬件设计和简单的软件编程,所以大大降低了开发难度。

FT245BL是FTDI公司的一款并行FIFO双向数据传输的USB芯片,对于微处理器它提供8位并行数据总线D0~D7,对于外部主机是标准串行总线或虚拟接口,其数据传输速率最高可达1 MB/s,提供USBl.1/2.O规范的全速物理接口,支持UHCI/OHCI/EHCI主控制器。

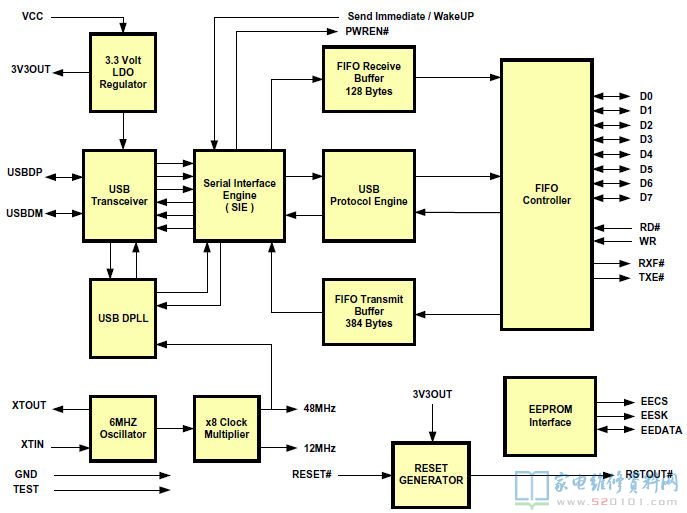

FT245BL芯片的内部系统结构框架图如上图所示,芯片主要由3.3V稳压器、USB收发器、串行接口引擎(SIE)、USB协议引擎和先进先出(FIFO)控制器、6 MHz振荡器、8×倍频器、USB锁相环、复位器、E。PROM接口等构成。其内部设置了2个FIFO数据缓冲区,一个是128 B的接收缓冲区;一个是384 B的发送缓冲区。串行接口引擎用来完成USB数据的串/并双向转换;USB协议引擎用于管理来自USB设备控制端口的数据流,实现USB主机控制器需要的USB底层协议。

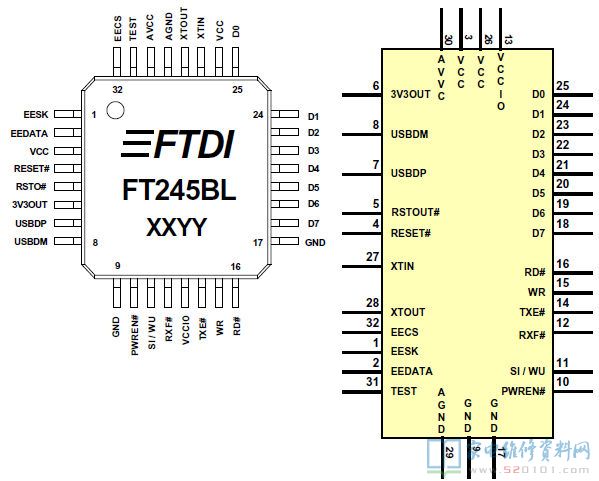

一、FT245BL引脚功能

二、FT245BL内部方框图

DSP与FT245BL接口框图如上图所示。主板CPLD用AMS[0:3]和高5位地址线(A19~A15)进行译码;FT245BL的TXE和RXF信号在查询地址有效时,通过DSP读取其状态,判断是否发送数据或接收数据;TXE用于判断发送FIFO是否满,0为不满,1为满,当TXE为0时,外部DSP向发送FIFO缓冲区写数据,直到发送数据全部写入;RXF用于判断接收FIFO是否有数据,只要数据个数≥1,RXF就为低,通知DSP可以读取数据。FT245BL的RD和WR信号在读写地址有效时,分别与DSP的ARE和AWE相连,DSP可以读取接收数据和写入发送数据。

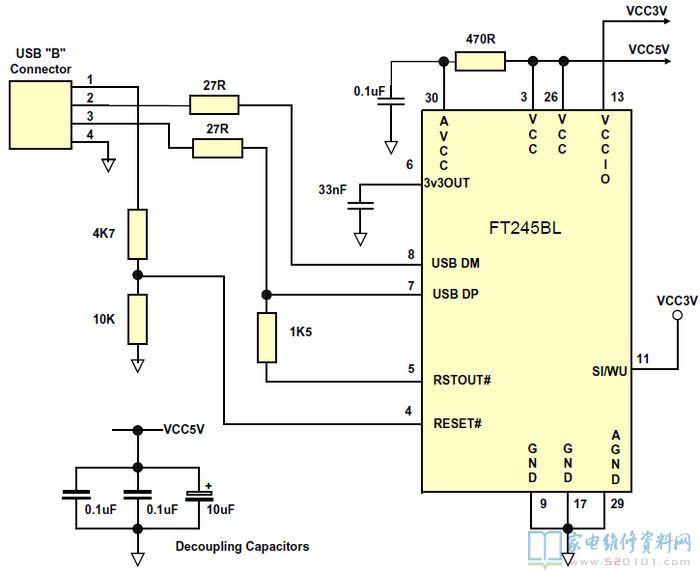

三、FT245BL典型应用电路(带3.3 V逻辑驱动/电源电压的自供电电路)

一个带有3.3V接口的USB自供电设计示例。在这种情况下,VCCIO由外部3.3V电源供电,以使设备IO引脚在3.3V逻辑电平下输出,从而允许其连接到3.3V MCU或其他外部逻辑。USB自供电设计使用自己的电源,并且不会从USB总线中获取任何电源。在这种情况下,不需要特别注意满足USB暂停电流(0.5 mA),因为设备无法从USB端口获得电源。

与总线供电的3.3V接口设计一样,在某些情况下,只需要少量电流(<5mA),可以使用FT245BL的内置调节器提供3.3V,而不需要任何其他组件。在这种情况下,将VCCIO连接到FT245BL的3V3输出引脚。请注意,如果不使用Si/WU,则应将其向上拉到VCCIO。

网友评论