一、问题现象:

近期平板产品(尤其是CORTTEZ机芯、MSTAR等机芯)出现了许多离散故障,主要表现为不开机、功能混乱、整机图像、声音异常、白平衡偏色等等,都是通过清空母块数据解决。

二、分析结论:

前期,MSTAR机芯为了解决母块失效问题,分别在VCC端增加存储器电源滤波电路、增加I/O口通过软件对写保护脚进行控制、更换EEPROM厂家等措施,但效果并不理想。通过分析(详见后续分析),这种现象的出现是一个复杂的系统问题;也就是整个方案软件、硬件组成的系统运行不稳定性造成的。对于系统的正常运行和可靠性而言,I2C总线时序是非常重要的。我们频繁的通断电,更对系统运行稳定性产生了负面影响。该问题的出现,并不能通过简单的硬件、应用软件的更改就能避免,需要方案厂家底层软、硬件设计人员对整个设计系统进行完善。EEPROM电路的硬件设计比较简单,CRT、平板大同小异,为什么会单单在某几个机芯方案中表现明显呢?CRT机芯表现比较稳定,这就很能说明问题。

对目前量产的机芯及正在开发的新方案,采取如下措施:

1、对量产的CORTEZ机芯、MSTAR机芯,在完检第一道工序增加清空母块操作;

2、对正在开发的机芯(120Hz项目)完善EEPROM、I2C系统硬件、软件设计:

1 对系统运行的稳定性、可靠性进行反复测试,完善底层软件的设计;

2 增加存储器电源滤波电路;

3 对通过I/O控制WP脚方式进行验证;

4 继续完善母块数据读取过程中的CHECKSUM校验。

在分析之初,也提出了诸如开机EEPROM初始化不完全、机内干扰脉冲改写EEPROM数据等原因,通过对EEPROM工作原理的分析,可以基本予以否定,下面将逐一进行分析。

三、存储器工作原理:

存储器(EEPROM)中不仅存储与普通电视相同的节目预选、音量、亮度、对比度等一些数据,还要存储各被控电路的调整数据和电路状态设置数据,例如:RF-AGC、白平衡、画中画、EMI、音量曲线设置,图像状态参数设置等等。

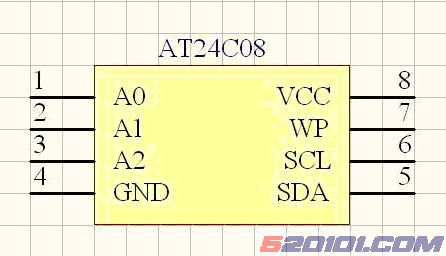

1、存储器(EEPROM)引脚定义:

8脚PDIP封装的24C××系列存储器引脚定义如下图所示,其中,A0、A1、A2为器件地址选择位,这三个引脚配置成不同的编码值,在同一串行总线上最多可扩展8片同一容量或不同容量的24C系列串行EEPROM芯片。WP(TEST)为硬件写保护控制端(测试端),SDA为串行数据输入/输出端,漏极开路驱动;容量扩展时,可以将多片24系列SDA引脚直接相连,实际使用时要加一个上拉电阻,VCC和GND分别是电源和地。

24C××系列存储器的⑦脚有两种接法:

美国AT、ST、BR公司生产的24C××系列存储器,其⑦脚需接地才能写入数据;而韩国KOA、KOR、KS公司生产的24C××系列存储器,其⑦脚则需接高电平才能写入数据。

2、存储器(EEPROM)上电过程中的映像操作及Checksum校验:

在系统的运行过程中,对EEPROM的任何读写操作,都是首先在其DDR中的映像缓冲RAM中完成的。EEPROM有一个字WORD存储Checksum值,即EEPROM各位做简单加法得到的值。当整机上电时,CPU首先在DDR中为EEPROM建立一同样容量的映像,同时对映像中的数据进行Checksum实时运算,将运算结果与EEPROM中的Checksum进行比较,如果结果不一致,CPU将对EEPROM进行初始化操作,我们所有的平板产品软件都做此处理。

这里,我们可以对先前的假设“开机对空EEPROM初始化不完全,导致某些电性能异常”进行分析。平板产品大部分机型在初次上电时,母块为空块,上电时CPU对母块执行初始化处理,即写入软件默认数据。如果在初始化时突然断电,母块数据没有写完全,这时还没有进行Checksum运算,Checksum值为0FFFFH;再次通电,CPU首先在DDR中为EEPROM建立一同样容量的映像,同时对映像中的数据进行Checksum实时运算,将运算结果与EEPROM中的Checksum进行比较,结果不一致,必定对EEPROM重新进行初始化,因此不会存在由于

EEPROM初始化不完全,导致某些电性能异常的故障。 [Page]

3、存储器(EEPROM)读写过程分析:

AT24CXX系列的EEPROM为了提高写效率,提供了页写功能,内部有个一页大小的写缓冲RAM,地址范围当然就是从00到一页大小,发生写操作时,开始送入地址对应的页被选中,并将其内容映像到缓冲RAM,数据从低端地址对应的缓冲RAM地址开始修改,超过这个地址范围就回到00;写完后,就会把开始确定的EEPROM页擦除,再把一整页RAM数据写入,所有写数据都发生在开始写地址时确定的页上。

如页容量为128,一页都是从00开始按128字节分成一个个的页,0页就是0~7F,1页就是80~FF,依次类推,边界就是128字节的整数倍地址。页RAM的地址范围为7位00~7F,写入时高端地址就是页号。发生写操作,开始送入地址对应的页被锁存,后续不论写多少,都在这个页中,只是一个页内的地址进行加一,超过就归零开始。页是绝对的,按整页大小排列,不是从开始写入的地址开始算。

读没有页的问题,可以从任意地址开始读取任意大小数据,只是超过整个存储器容量时地址才回卷,但一次性访问的数据长度也不要太大;所以分页的存储器要做好存储器管理,尽量同时读写的数据放在一个页上。

写完后,等待10ms以上时间再进行其它操作。关于WP脚(#7脚)写保护脚,它直接控制内部编程电压的升压泵工作。一定注意,当一次写操作完毕后,不能立即抬高这个引脚写保护,而应该等待10ms以上,内部操作完成后再置1。

由于干扰造成总线锁定问题,比如写操作时,由于干扰波形很差丢失一个SCL,这样就会在第9个SCL读不到应答,而在第9个SCL的下降沿,设备才输出应答锁定SDA=0;这样就会造成总线锁定,而使主设备无法发送停止位等等类似情况,会造成下面的操作出错。

从以上也可以看出,离散干扰脉冲要想完成对EEPROM的写操作也是很难的,首先干扰脉冲要能够对挂在I2C总线上的SLAVE器件完成寻址,并且对需要写入的页地址也要刚好对应,同时还要有写命令,这么多的巧合几率非常小。因此,对于“机内干扰脉冲改写EEPROM数据导致某些电性能异常”的分析不是不可能,只是出现的几率非常小。

对于这个问题,可以通过对EEPROM写保护脚进行设置解决,有两种方法:

(1)通过CPU一个端口控制存储器⑦脚电平,对其进行读写操作时,将⑦脚置于低电平,其余时间均将⑦脚置于高电平。这样即使总线受到信号干扰,也不能对存储器的数据造成影响。此方案优点是可用软件控制,灵活性较强,缺点是需要占用CPU一个I/O口,软

件需要对EEPROM的每次写操作进行控制,增加工作量;同时,在写入及对I/O的控制时序上会出现问题。MSTAR机芯在解决母块失效问题时采用过此方法,但效果并不理想,时序总出现问题,后来取消了。

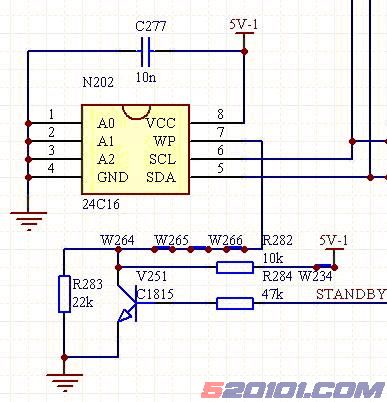

(2)在存储器⑦脚增加保护电路:(如下图所示)

将CPU待机控制端STANDBY引出一路接三极管V251基极,整机加上220V交流电后,CPU进行初始化及各项检测,然后CPU将STANDBY脚输出高电平,三极管导通后,将存储器⑦脚置于低电平,可以对存储器写入数据,此前STANDBY脚一直为低电平,存储器⑦脚置于高电平,不能对存储器进行读写,避免了交流开关机瞬间造成的脉冲干扰进入总线,从而保护了存储器中的数据,此方案在CRT瑞萨机芯中已批量应用。

网友评论