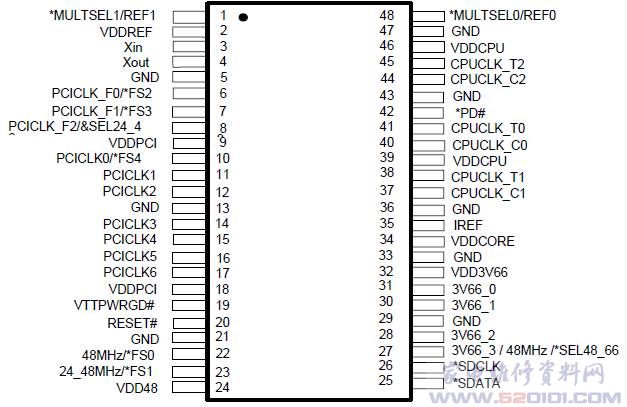

概述:W83194BR-323采用贴片48脚封装。

一、W83194BR-323引脚功能

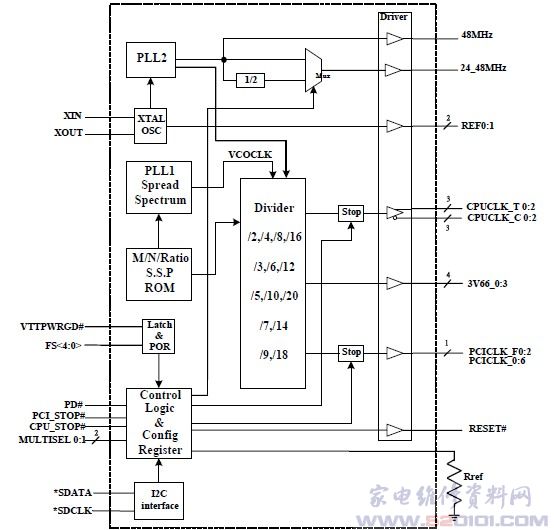

MULTSEL1/REF1、MULTSEL0/REF0: CPU时钟振幅设置/14.318MHz基本时钟输出。

VDDREF、VDDPCI、VDD48、VDD3V66、VDDCORE、VDDCPU: 3.3V电源输入。

GND:接地。

Xin:晶振输入。

Xout:品振输出。

PCICLK_F0/FS2、PCICLK_F1/FS3:3.3V自由运行PCI时钟输出/频率选择锁存器输入引脚。

PCICLK_F2/&SEL24_48:3.3V自由运行PCI时钟输出/锁存器选择输入引脚,设置48MHz或24MHz输出。

PCICLK0/FS4: PCI时钟输出/频率选择锁存器输入引脚。

PCICLK1至PCICLK6: PCI时钟输出。

VTTPWRGD#:电源好信号输入,低电平有效(芯片选通)。

RESET#:复位信号。

48MHz/FS0: 48MHz时钟输出/频率选择锁存器输入引脚。

24_48MHz/FS1: 24MHz或48MHz时钟输出/频率选择锁存器输入引脚。

SDCLK、SDATA: IIC总线。

3V66_3/48MHz/SEL48_ 66:3V66-3或48MHz时钟输出/锁存器选择输入引脚,设置48MHz或66.66MHz输出。

3V66_0至3V66_2:3.3V 66MHz时钟输出。

IREF:建立基准电流。

CPUCLK_T0至CPUCLK_T2: CPU时钟输出。

CPUCLK_C0至CPUCLK_C2: CPU时钟输出。

PD#:进入掉电状态,低电平有效。

网友评论