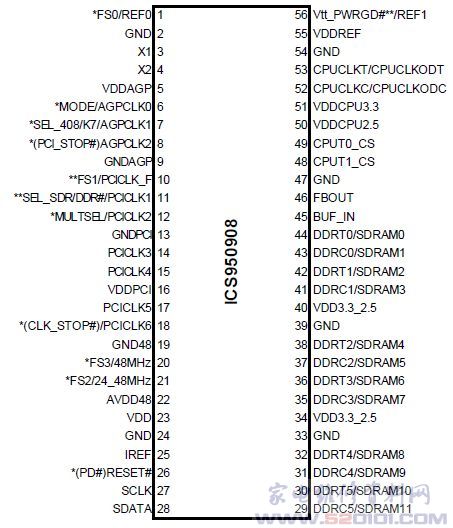

概述:ICS950908采用贴片56脚封装。

一、ICS950908引脚功能

VDDREF、 AVDD48、 VDDPCI、 VDD、 VDDAGP、 VDDCPU3.3: 3.3V电源输入。

VDDCPU2.5: 2.5V电源输入。

VDD3.3 2.5:3.3V或2.5V电源输入。

GND、GNDAGP、GNDPCI、GND48:接地。

X1:晶振输入。

X2:晶振输出。

MODE/AGPCLK0:功能选择锁存器输入引脚,1=桌面模式,0=移动模式/AGP时钟输出。

SEL 408/K7/AGPCLK1:CPU输出类型选择锁存器输入引脚,O=K7,1=CK408/AGP时钟输出。

(PCI STOP#)/AGPCLK2:暂停PCI时钟/AGP时钟输出。

FS1/PCICLK F:频率选择锁存器输入引脚/3.3V PCI自由运行时钟输出。

SEL SDR/DDR#/PCICLK1: 内存类型选择锁存器输入引脚,0=DDR, 1=PC133SDRAM/3.3V PCI时钟输出。

MULTSEL/PCICLK2:CPU时钟振幅设置/3.3V PCI时钟输出。

PCICLK3至PCICLK5:3.3V PCI时钟输出。

(CLK STOP#)/PCICLK6:暂停所有时钟/3.3V PCI时钟输出。

FS3/48MHz:频率选择锁存器输入引脚/3.3V 48MHz时钟输出。

FS2/24 48MHz:频率选择锁存器输入引脚/24MHz或48MHz时钟输出。

IREF:建立基准电流,通常接一475Ω电阻至地。

(PD#)/RESET#:使设备进入低功耗状态,低电平有效/复位信号。

SCLK、SDATA:IIC总线。

DDRT0/SDRAM0、DDRT1/SDRAM2、DDRT2/SDRAM4、DDRT3/SDRAM6、DDRT4/SDRAM8、DDRT5/SDRAM10:DDR时钟输出/3.3V SDRAM时钟输出。

DDRC0/SDRAM1 、 DDRC1/SDRAM3、 DDRC2/SDRAM5、 DDRC3/SDRAM7、DDRC4/SDRAM9、DDRC5/SDRAM11: DDR时钟输出/3.3V SDRAM时钟输出。

BUF IN:输入缓冲为内存输出。

FBOUT:内存反馈输出。

CPUTO CS、CPUTI CS: CPU时钟,2.5V推挽输出。

CPUCLKT/CPUCLKODT: CPU时钟,开放漏极外部1.5V推挽输出/2.5V CPU时钟输出。

CPUCLKC/CPUCLKODC: CPU时钟,开放漏极外部1.5V推挽输出/2.5V CPU时钟输出。

Vtt PWRGD#/REF1:电源好信号输入,低电平有效(芯片选通)/14.318MHz基本时钟。

网友评论