串行数据通信允许简化布局,需要较少的电路板面积用于布线,同时允许灵活地横跨模拟和数字边界进行布线。在噪声敏感应用中,串行接口在数字和模拟电路之间提供有效的隔离势垒,用于消除数字输出之间的耦合,以减少数字反馈。

采用 8b10b 编码、依据用于数据转换器的 JEDEC 串行接口规范 (JESD204) 对 LTC2274 的输出数据进行串行处理,并与很多 FPGA 高速接口兼容,如 Xilinx 公司的 Rocket IO、ALTEra 公司的 Stratix II GX I/O 和 LattICe 公司的 ECP2M I/O。LTC2274 以 2.1Gbps 速率通信,在目前市场上的所有 ADC 中,这是速率最快的高速串行接口。尖端通信设备、多通道系统、空间受限设计和仪表等应用都会得益于 LTC2274 独特的接口和丰富的功能。

LTC2274 具有几种独特的功能,可改善系统总体设计。就高灵敏度接收器应用而言,LTC2274 提供了一个内部透明的高频抖动电路,在低电平输入信号时,可将 ADC 的 SFDR 响应改善为远好于 100dBc。为了避免来自串行数字输出的干扰,该器件提供一个可选的数据扰码器,以使串行链路频谱随机化。还提供串行测试码型以方便串行接口测试。LTC2274 可以 105Msps 的最大采样率工作,内部 PLL 可以配置为锁定在 3 个不同的采样率范围之一。采用片上时钟占空比稳定器电路,是为了方便以非 50% 时钟占空比周期工作。为模拟和数字部分提供单独的停机引脚以节省功率。

在基带具有卓越的 77.5dB 信噪比(SNR) 性能和 100dB 无寄生动态范围 (SFDR)。80fsRMS 的超低抖动以极高的噪声性能实现了高达 500MHz 的输入频率欠采样。采用3.3V 模拟电源,消耗 1.3W 功率。

一、LTC2274特性

高速串行接口(JESD204)

采样速率:105Msps

77.7dBFS噪声层

100dBSFDR

在250MHz时的SFDR>82dB(1.5VP-P输入范围)

PGA前端(2.25VP-P或1.5VP-P输入范围)

700MHz满功率带宽S/H(采样及保持)

任选的内部高频颤动

单3.3V电源

功耗:1300mW

时钟占空比稳定器

引脚兼容系列:105Msps

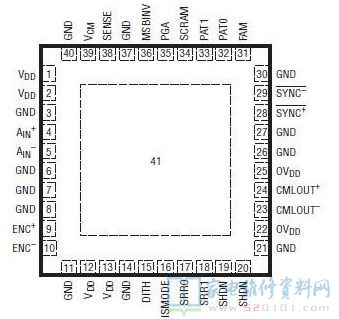

二、LTC2274引脚功能

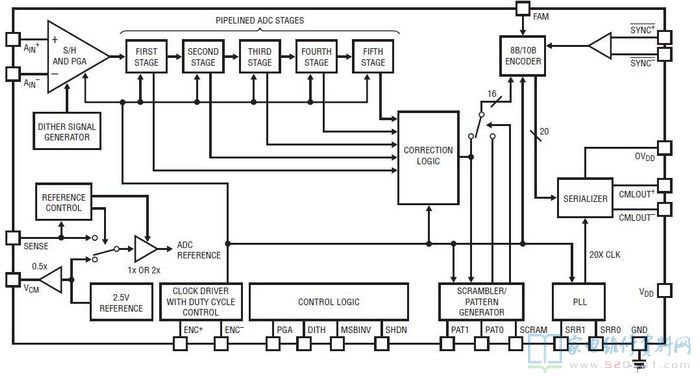

三、LTC2274内部方框图

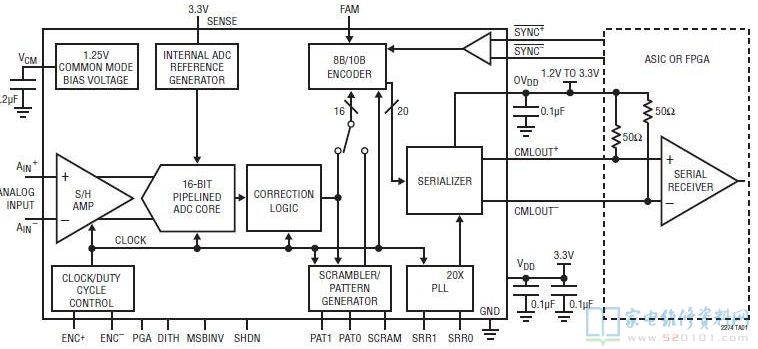

四、LTC2274典型应用电路

网友评论