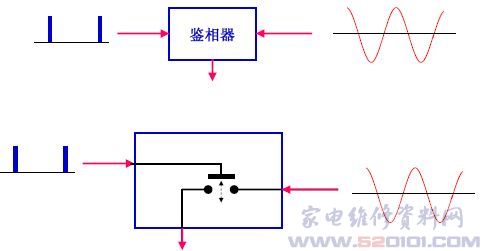

什么是锁相环(PLL)电路

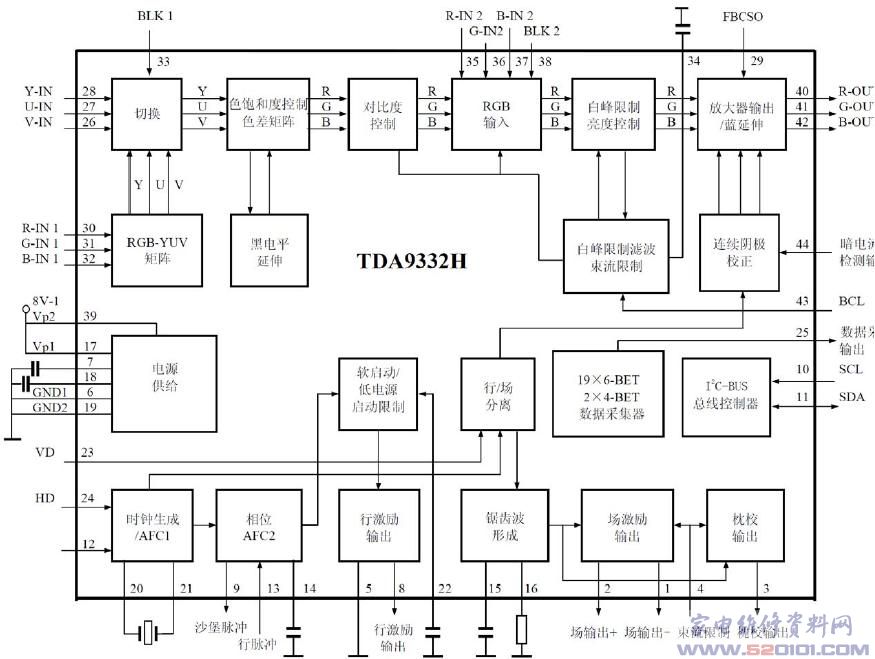

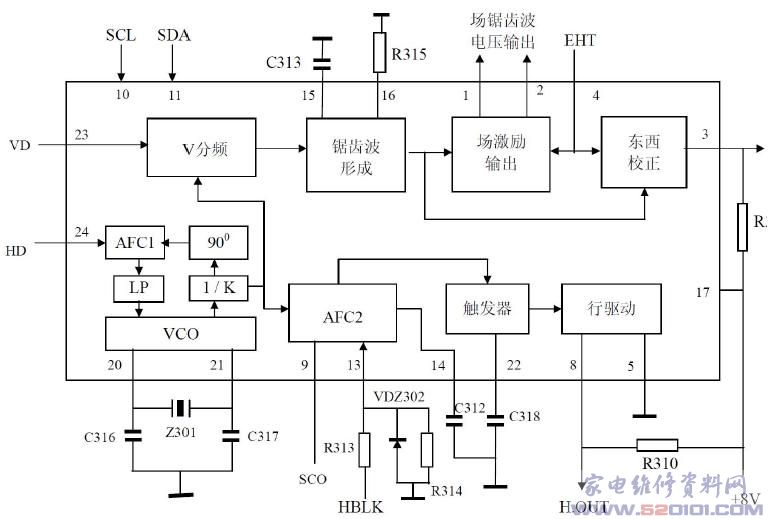

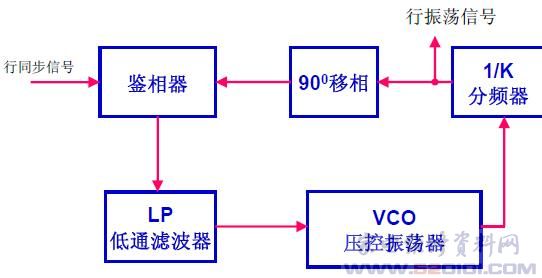

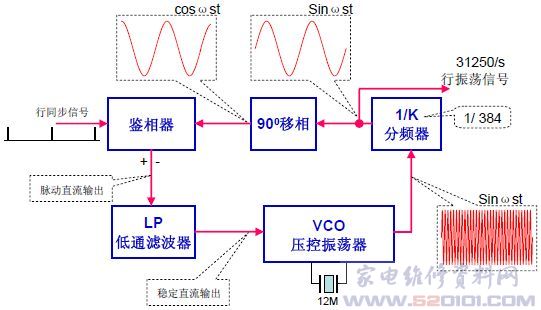

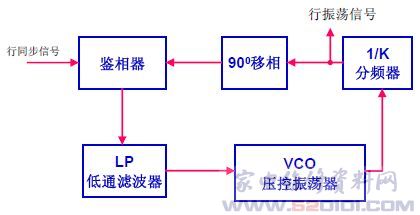

锁相环(phase-locked loop)为电器设备中使频率振荡器;振荡频率稳定的一种电路,主要有VCO(压控振荡器)、移相电路、鉴相电路及低通滤波器电路组成,压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与同步信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则鉴相器的电压输出端的电压发生变化,去控制VCO,直到相位差恢复!达到锁频的目的!!能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

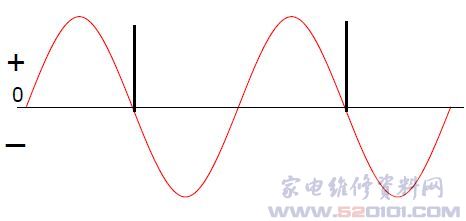

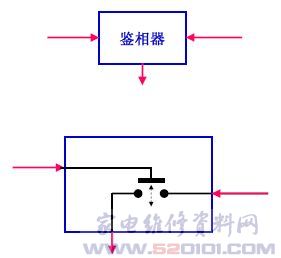

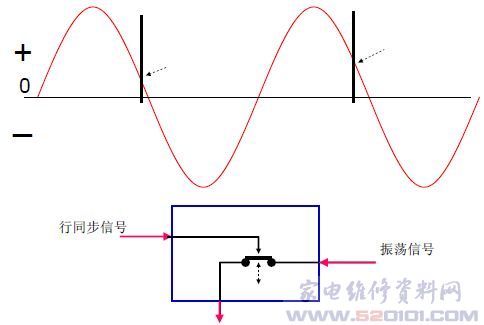

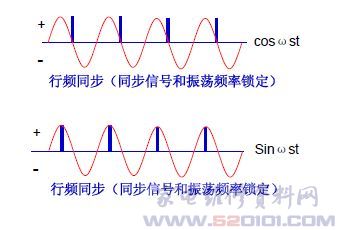

行同步信号锁定振荡频率时:每一个行同步信号都落在振荡信号(经过900移相)的零点处

同步头出现瞬间振荡信号正好过0 点那么;开关瞬间接通,此时输出端,输出为0

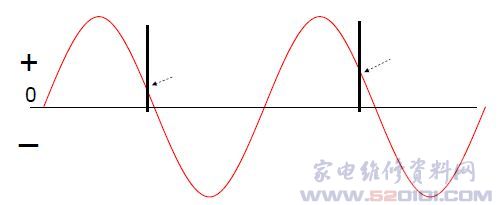

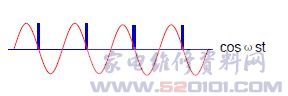

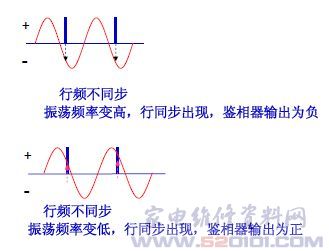

行同步信号不同步,振荡频率变高时:行同步信号落在振荡信号的负半周位置上。

同步头出现瞬间振荡信号正好落在振荡信号负半周那么;开关瞬间接通,此时输出端,输出为负

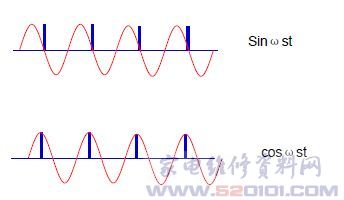

行同步信号不同步,振荡频率变低时:行同步信号落在振荡信号的正半周位置上。

网友评论