存储器是一种具有记忆功能的接收、保存和取出信息的设备,是计算机的重要组成部分,是CPU最重要的系统资源之存储器按在微机中的位置可分为主存储器(内存)、辅助存储器(外存)和缓冲存储器(缓存)三大类。内存一般由半导体存储器构成,通常装在计算机主板上,存取速度快,但容量有限;外存是为了弥补内存容量的不足而配置的,如硬盘、软盘等,外存容量大、成本低,所存信息既可修改也可长期保存,但存取速度慢;缓存位于内存与CPU之间,其存取速度非常快但存储容量更小,一般用来解决存取速度与存储容量之间的矛盾,可提高整个系统的运行速度。存储器主要性能指标是存储容量、存储速度和可靠性。

一、随机存取存储器RAM

计算机的内存储器由ROM和RAM两部分组成。其中,只能读不能写的存储器,称为只读存储器ROM;即能读又能写的存储器,叫做可读写存储器RAM。由于历史上的原因,可读写存储器也被人们称为随机存取存储器。

通常ROM中的程序和数据是事先存人的,在工作过程中不能改变,这种事先存人的信息不会因掉电而丢失,因此ROM常用来存放计算机监控程序、基本输入输出程序等系统程序和数据8RAM中的信息则掉电就会消失,所以主要用来存放应用程序和数据。

对存储器的读写或取出都是随机的,通常要按顺序随机存取。按顺序随机存取有两种方式: 一是先进先出;二是后进先出。

1.RAM的功能与结构

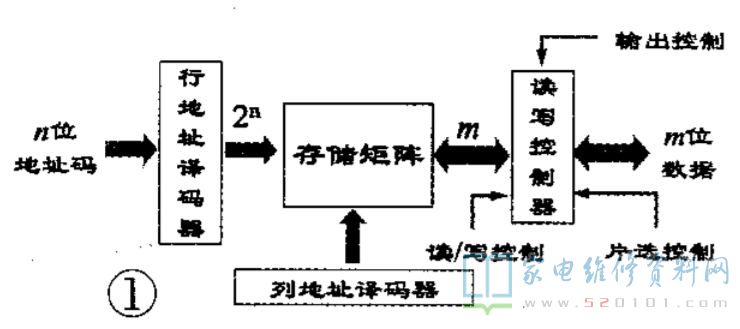

RAM的电路结构框图如图1所示。地址译码器:RAM中的每个寄存器都有一个编号,称为地址。在每次读/写信息时,只能和某一一个指定地址的寄存器之间进行取出或是存入,此过程称为访问存储器。访问地址的是机器识别的二进制数,送给地址译码器译码后,由相应输出线给出信号,控制被选中的寄存器与存储器的I/O端子,使其进行读/写操作。

I/O控制器:为了节省器件引脚的数目,数据的输人和输出共用相同的I/O引脚。读出时它们是输出端,写人时它们又是输入端,即一线二用,由读/写控制线控制。I/O端子数决定于一一个地址中寄存器的位数。通常RAM中寄存器有五种输人信号和一种输出信号:地址输入信号、读/写控制输人信号、OE输出控制信号、CS片选控制输入信号、数据输人信号和数据输出信号。

片选控制:由于集成度的限制,通常要把许多片RAM组装在一起构成一台计算机的存储器。当CPU访问存储器时,存储器中只允许一片RAM中的一个地址与CPU交换信息,其他片RAM不能与CPU发生联系,所谓片选就是实现这种控制。通常一片RAM有1根或几根片选线,当某一片的片选线为有效电平时,则该片被选中,地址译码器的输出信号控制该片某个地址与CPU接通;片选线为无效电平时,与CPU之间呈断开状态。例如片选信号CS=“1"时,RAM禁止读写,处于保持状态,I/O口的三态门处于高阻抗状态;CS="0”时,RAM可在读/写控制输人R/W的作用下作读出或写人操作。

存储矩阵:存储矩阵是存储器的主体,含有大量的基本存储单元。通常数据和指令是用-定位数的二进制数来表示的,这个二进制数称为字,字的位数称为字长。存储器以字为单位进行存储,为了存人和取出的方便,必须给每个字单元以确定的标号,这个标号称为地址,不同的字单元具有不同的地址。存储器的容量由地址码的位数m决定,当地址码的位数为n,长的位数为m时,存储器内含2nXm个存储单元。

2.RAM的存储单元电路

存储单元是RAM的核心部分,RAM字中所含的位数是由具体的RAM器件决定的,可以是4位、8位、16位和32位等。每个字是按地址存取的。一般操作顺序是:先按地址选中要进行读或写操作的字,再对找到的字进行读或写操作。打一比方:存储器好比一座宿舍楼,地址对应着房间号,字对应着房间内住的人,位对应床位。

存储器按功能的不同可分为静态和动态两类,按所用元件的类型又可分为双极型和单极型两种。双极型存储单元速度快,单极型存储单元功耗低容量大。在要求存取速度快的场合常用双极型RAM电路;在对速度要求不高的场合,常用单极型存储器。下面主要以单极型存储器为例介绍RAM的工作原理。

(1)静态RAM存储单元

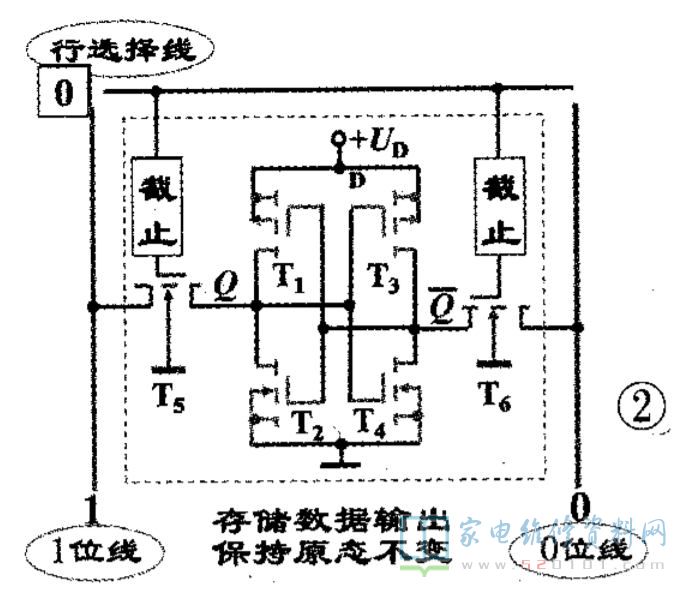

T1和T2、T3和T4分别构成两个反相器,如图2所示。两个反相器交叉耦合又构成了基本触发器,作为储存信号的单元,当Q=1时为“1”态,Q=0时为“0”态。T5和T6是门控管,其导通和截止均受行选择线控制。

当行选择线为高电平时,T5、T6导通,触发器输出端与位线接通;当行选择线为低电平时,T5、T6截止,存储单元和位线断开。

(2)动态RAM存储单元

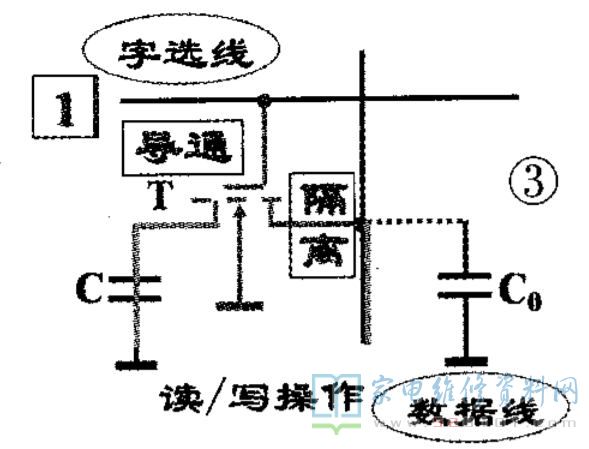

一个MOS管和一个电容即可组成一个最简单的动态存储单元电路,如图3所示。

写入时,送到数据线上的二进制信号经T存人C中;读出时,C的电平经数据线读出,读出的数据经放大后,再送到输出端。

由于C和数据线的分布电容Co相并,因此C要损失部分电荷。为保持原有信息不变,使放大后的数据同时回送到数据线上,对C应进行重写,称为刷新。对长时间无读/写操作的存储单元,C会缓慢放电,所以存储器必须定时对所有存储单元进行刷新,这是动态存储器的特点。

3.RAM的容量扩展

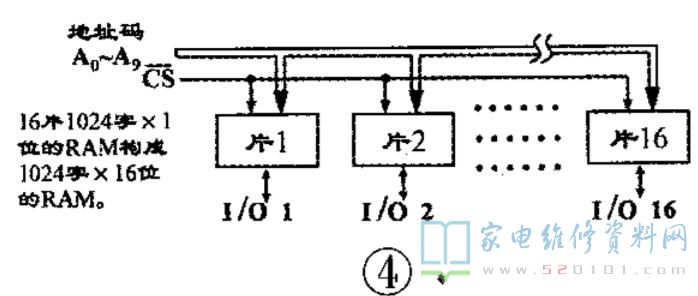

RAM的容量由地址码的位数n和字的位数m共同决定。因此常用的容量扩展法有位扩展、字扩展和字位扩展三种形式。如果一片RAM中的字数已经够用,而每个字的位数不够用时,可采用位扩展连接方式解决。其数据位的扩展方法是将各个RAM的地址码并联,片选端并联,如图4所示。

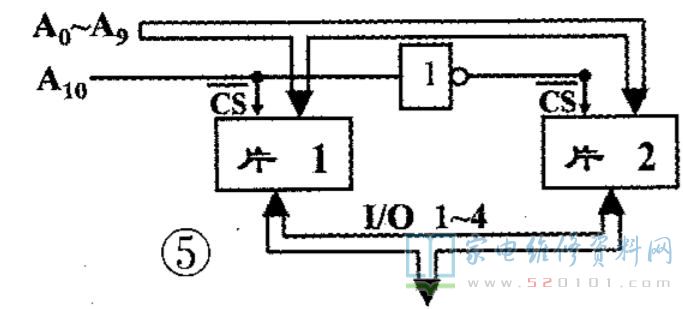

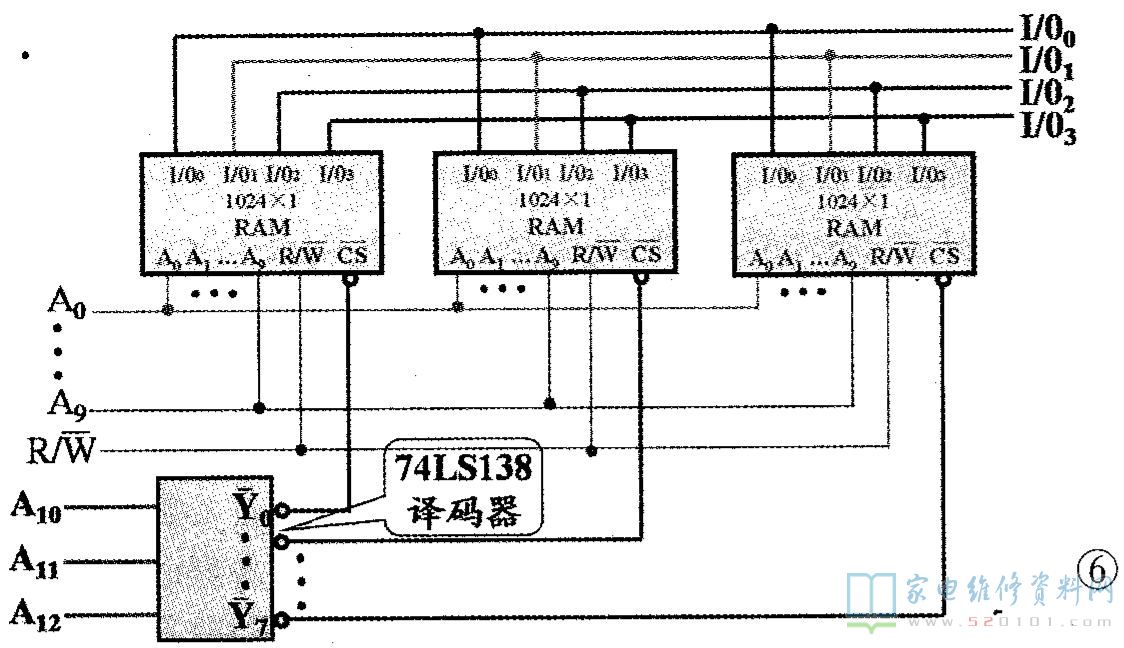

图5所示为RAM字扩展的典型实例:利用两片1024字x4位的RAM器件构成2048字x4位的RAM。利用地址码的最高位A10控制RAM器件的片选Cs端,以决定哪一片RAM工作。地址码的低A0~A9并联接到两片RAM的地址输人端。两片RAM的数据输人/输出端(I/O 1~4)按位对应地并联使用。字位同时扩展连接较复杂,如图6所示。

16片1024X4位的RAM和3线-8线译码器74IS138相接,可扩展三个地址输人端,构成一个8kx4位的RAM。

二、 可编程逻辑器件

可编程逻辑器件属于只读存储器ROM,其方框图与RAM相似。

ROM将RAM的读写电路改为输出电路;ROM的存储单元由一些二极管、MOS管及熔丝构成,结构比较简单。

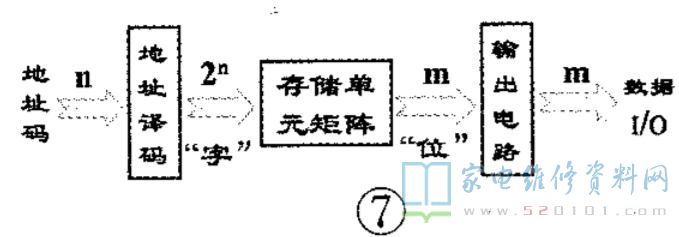

1.只读存储器ROM的基本结构

只读存储器在工作时只能进行读出操作,基本结构如图7所示。只读存储器ROM的特点是:存储单元简单,集成度高,且掉电时数据不会丢失。

2.可编程逻辑器件的存储单元

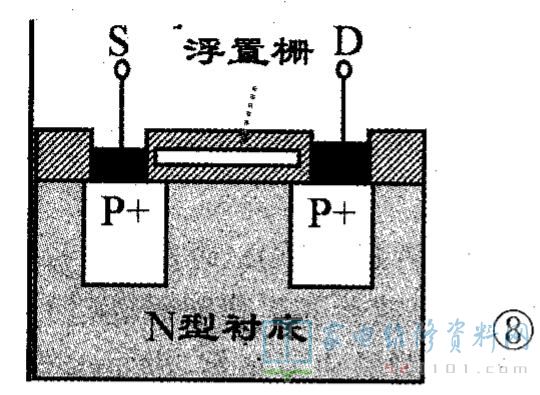

只读存储器ROM存人数据的过程称为“编程”。根据编程方式的不同,可分为内容固定的ROM,一次性编程的PROM、可多次编程的EPROM和电改写的EEPROM。早期制造的PROM可编程逻辑器件的存储单元是利用其内部熔丝否被烧断来写人数据的,因此只能写人一次,使其应用受到很大限制。目前使用的PROM可多次写人,其存储单元是在MOS管中置人浮置栅的方法实现的。

浮置栅型PMOS管的结构原理图如图8所示,浮置栅被包围在绝缘的二氧化硅之中。写人时,在漏极和衬底之间加足够高的反向脉冲电压把PN结击穿,雪崩击穿产生的高能电子穿透二氧化硅绝缘层进入浮置栅中。脉冲电压消失后,浮置栅中的电子无放电回路而被保留下来。

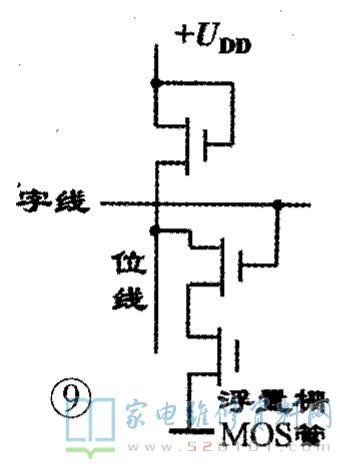

浮置栅PMOS写入数据后,带电荷的浮置栅使PMOS管的源极和漏极之间导通,当字线选中某一存储单元时,该单元位线即为低电平,如图9所示;若浮置栅中无电荷(未写入),浮置栅PMOS管截止,位线为高电平。当用户需要改写存储单元中的内容时,要用紫外线或X射线照射擦除,使浮置栅上注人的电荷形成光电流泄漏掉,EPROM可恢复原来未写人时的状态,因此又可重新写人新信息。

利用光照抹掉写人内容需要大约30min的时间。为了缩短抹去时间,人们研制出了电擦除方式。电擦除的速度一般为ms数量级,其擦除的过程就是改写的过程,改写以字为单位进行的。电擦除的EEPROM既可以在掉电时不丢失数据,又可以随时改写写,人的数据,重复擦除和改写的次数可达1万次以上。

3.可编程逻辑器件

可编程逻辑器件常简称为PLD( programmable logic device ) ,按编程方式可分为掩膜编程和现场编程。掩膜编程是由生产厂家采用掩膜工艺专门为用户制作;现场编程则是由用户在工作现场进行编程,以实现所需要的逻辑功能。

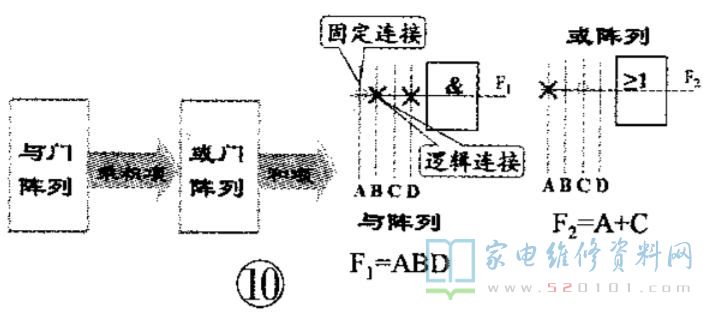

任意一个逻辑函数都可以写成与一或表达形式,所以可编程逻辑器件的基本结构是一个 与阵列和一个或阵列,如图10所示。

PLD有较大的与或阵列,其逻辑图的画法也与传统的画法有较大的区别。

(1)可编程逻辑阵列(PLA)

可编程逻辑阵列PLA在存储器中的主要应用是构成组合逻辑电路中,例如可用PLA实现4位二进制数转换为Gray码(格雷码,又叫循环二进制码或反射二进制码)的电路。

PLA的特点:与阵列和或阵列都可以编程。PLA中的与阵列被编程产生所需的全部与项;PLA中的或阵列被编程完成相应与项间的或运算并产生输出,如图11所示。

PLA大大提高芯片面积的有效利用率。

(2)可编程阵列逻辑(PAL)

可编程阵列逻辑PAL的速度高且价格低,电路输出结构形式有多种,因此可以方便地进行现场编程,所以大受用户欢迎。

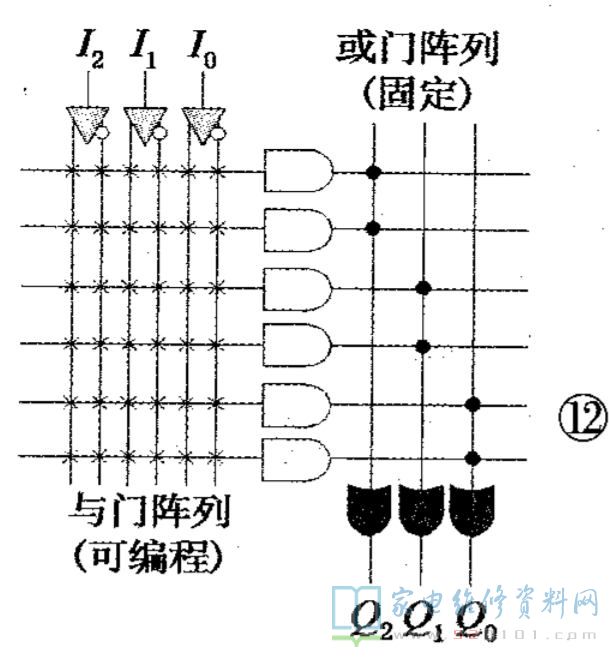

为实现时序逻辑电路的功能,可编程阵列逻辑PAL在或门和三态广之间加人D触发器,并且将D触发器的输出反馈回与阵列,如图12所示,从而使PAL的功能大大提高。与同样位数的PLA相比,PAL不但减少了编程点数,而且也简化了编程工作,更加有利于辅助设计系统的开发。

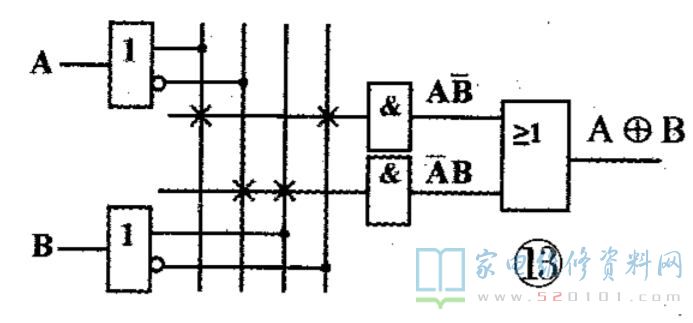

PAL编程是按“熔丝图”进行的,图13所示为实现“异或”函数的熔丝图,图中“x”表示熔丝保留,而无“x”的交点表示熔丝烧断。

由于PAL采用双极型熔丝工艺,工作速度较高,但由于与阵列的“熔丝”工艺,因此只能进行一次编程,而且需要在专门的编程器上进行编程,所以其应用仍受到限制。

网友评论